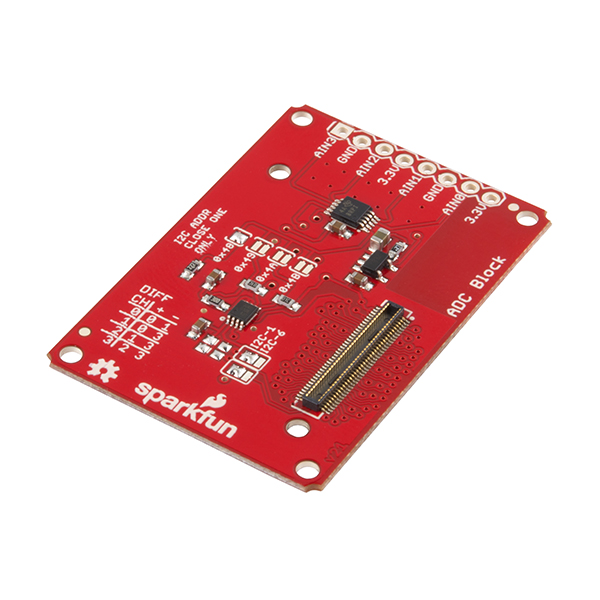

SparkFun Block for Intel Edison - ADC (DEV-13770)

This card adds ADC functionality to the Edison's I2C bus. The ADS1015 ADC from TI provides a single 12-bit delta-sigma convertor with an analog multiplexer. It can be configured as a four-channel single-ended device or as a two-channel differential device.

The board has jumpers to allow selection of the I2C slave address among four different options, allowing up to four of these cards to be stacked under one Edison. The sampling rate is not sufficient for audio capture, at 2.2kHz, but it should be adequate for most control applications.

- /Hardware - Eagle design files (.brd, .sch)

- /Production - Production panel files (.brd)

- Hookup Guide - Basic hookup guide for the Edison ADC Block.

- SparkFun Fritzing repo - Fritzing diagrams for SparkFun products.

- SparkFun 3D Model repo - 3D models of SparkFun products.

- v21 - Version 2.1. Currently for sale. Fixes noise on the ADC lines, adds locking header footprint.

- v20 - Version 2.0. Retired.

- v10 - Original release. Retired.

This product is open source!

Please review the LICENSE.md file for license information.

If you have any questions or concerns on licensing, please contact [email protected].

Distributed as-is; no warranty is given.

- Your friends at SparkFun.