Comments (6)

How do you initialize base field in meihap? how do you set up the interrupt vector table? what value do you get in t1 before jr t1? does it match with your interrupt handler start address?

can you single step your handler? can you get trace info from the CPU ( with logic analyzer)?

Can you simulate your code on RTL or ISS and get program trace ?

from cores-veer-eh1.

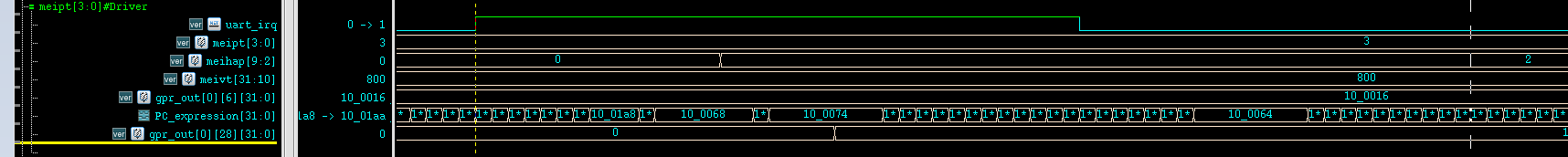

At the moment I simulate RTL only. Please, have a look at the waveform with the requested signals.Also attached are program code and its listing file.

issue50_listing.txt

issue50_program.txt

Register t3(x28) is used in the program insted t1. Before executing jr t3, t3 gets value 0x100016 - this is address of the desired interrupt handler (UART). So this looks correct.

MEIHAP gets value 2, this corresponds to uart_irq (level sensitive) connected to extintsrc_int[2]. The interrupt handler pointer (uart_handler) is stored in DCCM (offset 0x200000).

from cores-veer-eh1.

At the waveform PC_experssion jumps to 0x100016(uart_handler) after 0x100074. Next, CPU clears interrupt source UART_IRQ, but it takes quite many cycles. If I don't insert NOPs, MRET occurs early while UART_IRQ is still high. This is probably why MRET isn't executed.

from cores-veer-eh1.

from cores-veer-eh1.

you probably need to poll UART interrupt pending register and CPU MIP until no pending interrupts detected before exit the interrupt handler .. Remember, the UART may run on much slower clock than CPU so it can take quite a few CPU clocks to dis-assert interrupt request. Also there are a few CPU clocks for interrupt request signal to propagate to the core through PIC ...

from cores-veer-eh1.

At the waveform PC_experssion jumps to 0x100016(uart_handler) after 0x100074. Next, CPU clears interrupt source UART_IRQ, but it takes quite many cycles. If I don't insert NOPs, MRET occurs early while UART_IRQ is still high. This is probably why MRET isn't executed.

You must clear the IRQ source and validate that the IRQ has been cleared before executing MRET. Else the core will come right back into the handler if the input external interrupt pin is still high when the MRET executes.

Please open a new issue if you still have questions.

from cores-veer-eh1.

Related Issues (20)

- fpga_optimize cannot be set to 0 in swerv_config HOT 1

- openocd timeout occurs when trying to load elf file using command 'load_image'. HOT 7

- Try running multi thread program on swerv EH1 core HOT 2

- CoreMark test score HOT 2

- Unable to replicate performance improvement achieved by using different target values HOT 1

- Usage scenarios of different DFFs

- GHR refresh HOT 1

- Fusesoc's sim target is deprecated HOT 10

- Question about pipeline FF enable signals

- facing issues when C code size goes beyond 8KB HOT 1

- Coremark for new extension

- Repo renaming HOT 2

- Blocking Loads/DMA disable

- OpenOCD download to ICCM/DCCM failed. HOT 1

- The new feature of verilator stops building procession HOT 2

- Formal Verification of SweRV EH1 using riscv-formal

- GCC version in Makefile HOT 4

- $readmem file address beyond bounds of array HOT 8

- Timing violations with Vivado HOT 4

- slip in dec_decode_ctrl

Recommend Projects

-

React

React

A declarative, efficient, and flexible JavaScript library for building user interfaces.

-

Vue.js

🖖 Vue.js is a progressive, incrementally-adoptable JavaScript framework for building UI on the web.

-

Typescript

Typescript

TypeScript is a superset of JavaScript that compiles to clean JavaScript output.

-

TensorFlow

An Open Source Machine Learning Framework for Everyone

-

Django

The Web framework for perfectionists with deadlines.

-

Laravel

A PHP framework for web artisans

-

D3

Bring data to life with SVG, Canvas and HTML. 📊📈🎉

-

Recommend Topics

-

javascript

JavaScript (JS) is a lightweight interpreted programming language with first-class functions.

-

web

Some thing interesting about web. New door for the world.

-

server

A server is a program made to process requests and deliver data to clients.

-

Machine learning

Machine learning is a way of modeling and interpreting data that allows a piece of software to respond intelligently.

-

Visualization

Some thing interesting about visualization, use data art

-

Game

Some thing interesting about game, make everyone happy.

Recommend Org

-

Facebook

We are working to build community through open source technology. NB: members must have two-factor auth.

-

Microsoft

Open source projects and samples from Microsoft.

-

Google

Google ❤️ Open Source for everyone.

-

Alibaba

Alibaba Open Source for everyone

-

D3

Data-Driven Documents codes.

-

Tencent

China tencent open source team.

from cores-veer-eh1.