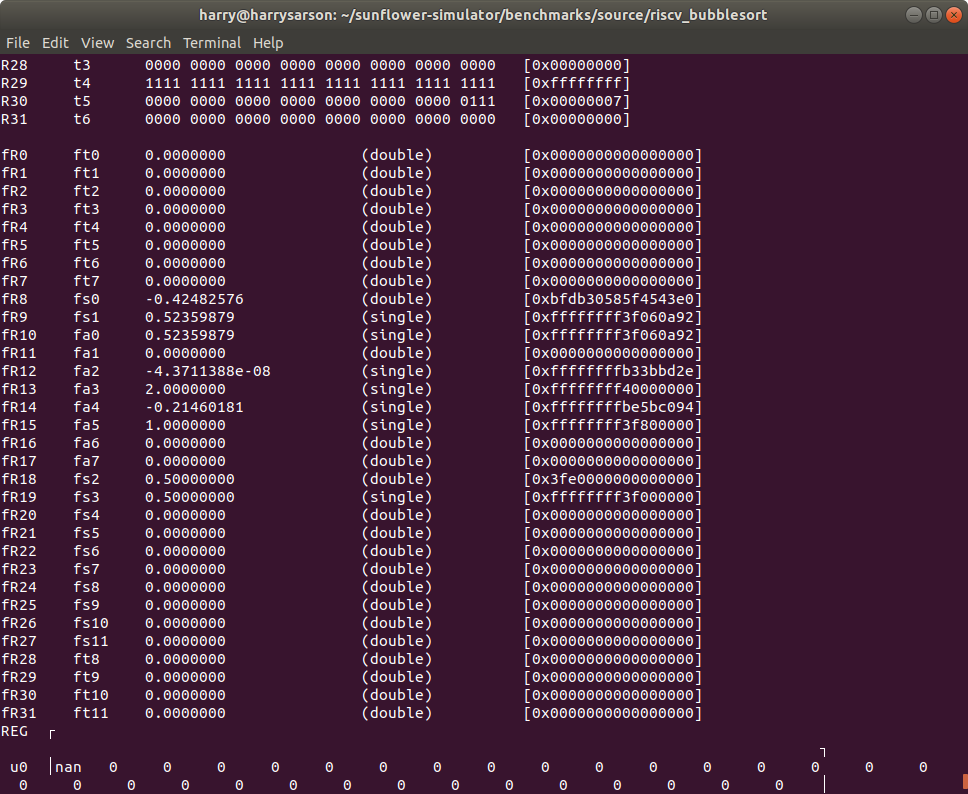

Sunflower is a full-system emulator for embedded sensing, computation, communication, fault modeling, power dissipation, batteries, and more. It is designed for use in research where you would normally need to have several embedded hardware systems networked over wired or wireless interfaces. Sunflower allows you to take compiled binaries and emulate them instruction by instruction, while emulating the effect of that computation on power dissipation, emulating the effect of the power dissipation on power regulators, modeling the effect of current drawn on electrochemical battery state of charge, and doing all of this for multiple complete embedded systems (tens or even hundreds) networked over wired or wireless networks or integrated into a single chip and communicating over shared memory.

Figure 1. An example of a system configuration that can be emulated in Sunflower.

The correct way to clone this repository to get the simulator and the submodules it depends on is:

git clone --recursive https://github.com/physical-computation/sunflower-embedded-system-emulator.git

To update all submodules:

git pull --recurse-submodules

git submodule update --remote --recursive

Checkout master branch and take each submodule out of the "Detached HEAD" state:

git submodule foreach git checkout master

Read the manual (sunflowersim-manual-and-cover.pdf) if you can. Dependencies: Building the simulator depends on GNU awk (gawk), on the GNU version of bison, the GNU version of sed, and libc6-dev-i386, so install them.

Edit conf/setup.conf to match your installation directory and system setup. On macOS, use the configuration:

OSTYPE = darwin

MACHTYPE = x86_64

On Linux, use the configuration

OSTYPE = linux

MACHTYPE = i386

To configure the emulator to default to RISC-V processor support rather than Hitachi SuperH, you will want:

TARGET = riscv

TARGET-ARCH = riscv32-elf

Set the paths to the GNU awk, GNU bison, and GNU sed in conf/setup.conf.

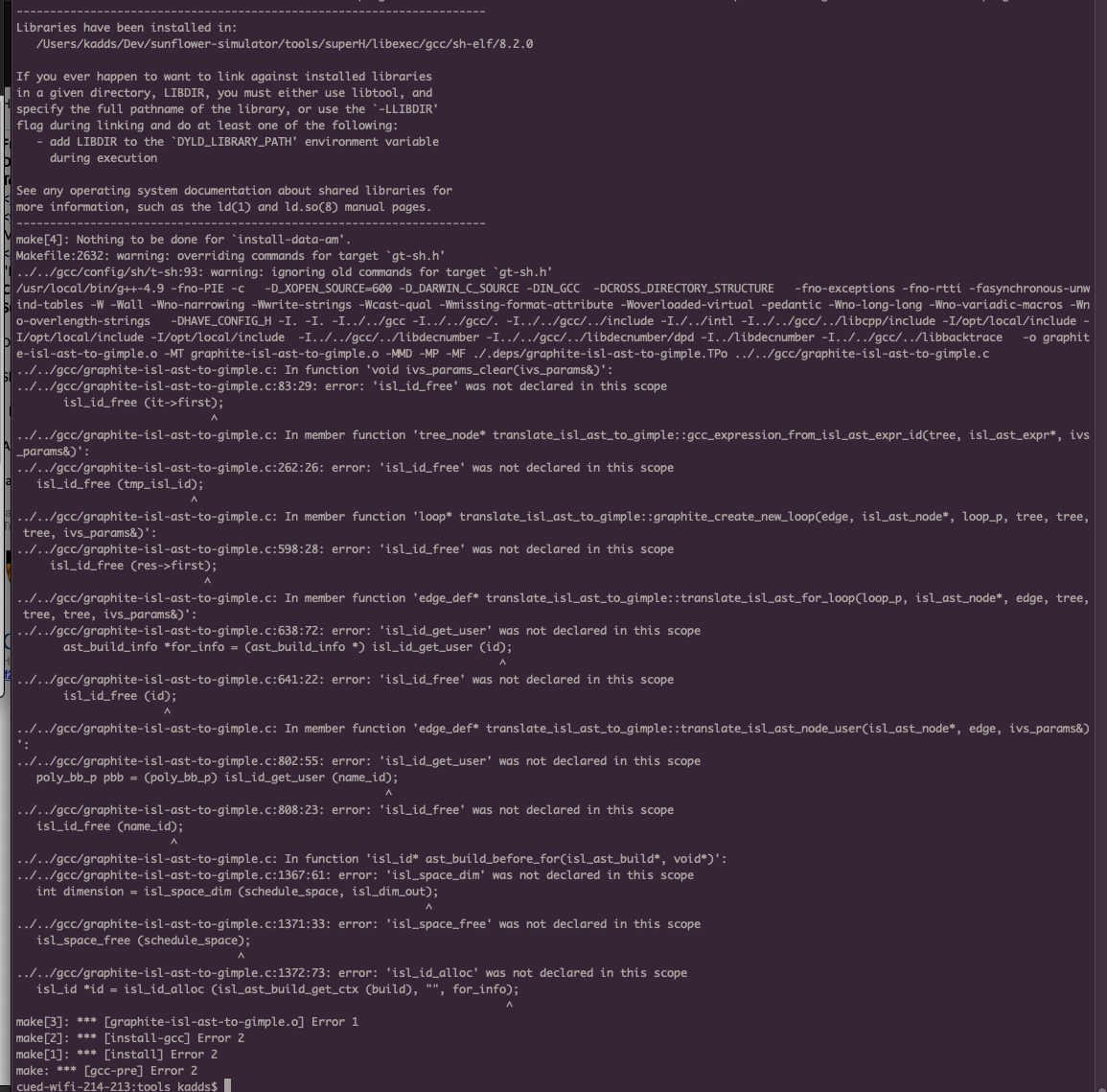

Once you have edited conf/setup.conf, follow the instructions below to build the cross-compiler:

- Change directory to

tools/sourcefrom the root of the Sunflower tree. - Run

./downloads.shin the directorytools/sourcerelative to the root of the Sunflower tree. This will download the source for various tools needed for building the cross-compilers. - From the root of the Sunflower tree, run

make cross-superHto build the Hitachi SH cross compiler ormake cross-riscvto build the RISC-V cross compiler.

If you have trouble building on macOS, you might be running into this issue.

The configuration file conf/setup.conf sets global configuration parameters needed by other tools, such as specifying what your workstation architecture is.

The conf/setup.conf configuration file does not influence which processor architectures Sunflower supports: Sunflower by default has support for all architectures enabled and you can create a simulation instance with multiple embedded systems each of a different architecture, all running simultaneously and interacting with each other. The default processor instances when you launch sim are SuperH. You can create RISC-V instances using the sunflower command newnode riscv. You can explicitly request SuperH instances using the command newnode superh. You can have a mix of SuperH and RISC-V processors in the same simulation (i.e., in the same launch of sim). From the simulator’s perspective, both architectures are always supported and it is not possible to purposefully configure the sim for one or the other.

To keep the emulator implementation independent of any third-part libraries, the Sunflower REPL does not integrate command history (e.g., using the readline library). If you want command history, use rlwrap.

Phillip Stanley-Marbell and Michael Hsiao. “Fast, Flexible, Cycle-accurate Energy Estimation”. In Proceedings of the 2001 International Symposium on Low Power Electronics and Design, ISLPED ’01. Huntington Beach, California, USA: ACM, pp. 141–146. ISBN: 1-58113-371-5. doi: 10.1145/ 383082.383120.

BibTeX:

@inproceedings{Stanley-Marbell:2001:FFC,

author = {Phillip Stanley-Marbell and Michael Hsiao},

title = {Fast, Flexible, Cycle-accurate Energy Estimation},

booktitle = {Proceedings of the 2001 International Symposium

on Low Power Electronics and Design},

series = {ISLPED '01},

year = {2001},

isbn = {1-58113-371-5},

location = {Huntington Beach, California, USA},

pages = {141--146},

numpages = {6},

publisher = {ACM},

address = {New York, NY, USA},

}

Phillip Stanley-Marbell and Diana Marculescu. “Sunflower: Full-system, Embedded, Microarchitecture Evaluation”. In Proceedings of the 2nd International Conference on High Performance Embedded Architectures and Compilers. HiPEAC’07. Ghent, Belgium: Springer-Verlag, pp. 168–182. ISBN: 978-3-540-69337-6.

BibTeX:

@inproceedings{Stanley-Marbell:2007:SFE,

author = {Phillip Stanley-Marbell and Diana Marculescu},

title = {Sunflower: Full-system, Embedded, Microarchitecture Evaluation},

booktitle = {Proceedings of the 2nd International Conference on

High Performance Embedded Architectures and Compilers},

series = {HiPEAC'07},

year = {2007},

isbn = {978-3-540-69337-6},

location = {Ghent, Belgium},

pages = {168--182},

numpages = {15},

publisher = {Springer-Verlag},

address = {Berlin, Heidelberg},

}